Welcome to Silicon Concept

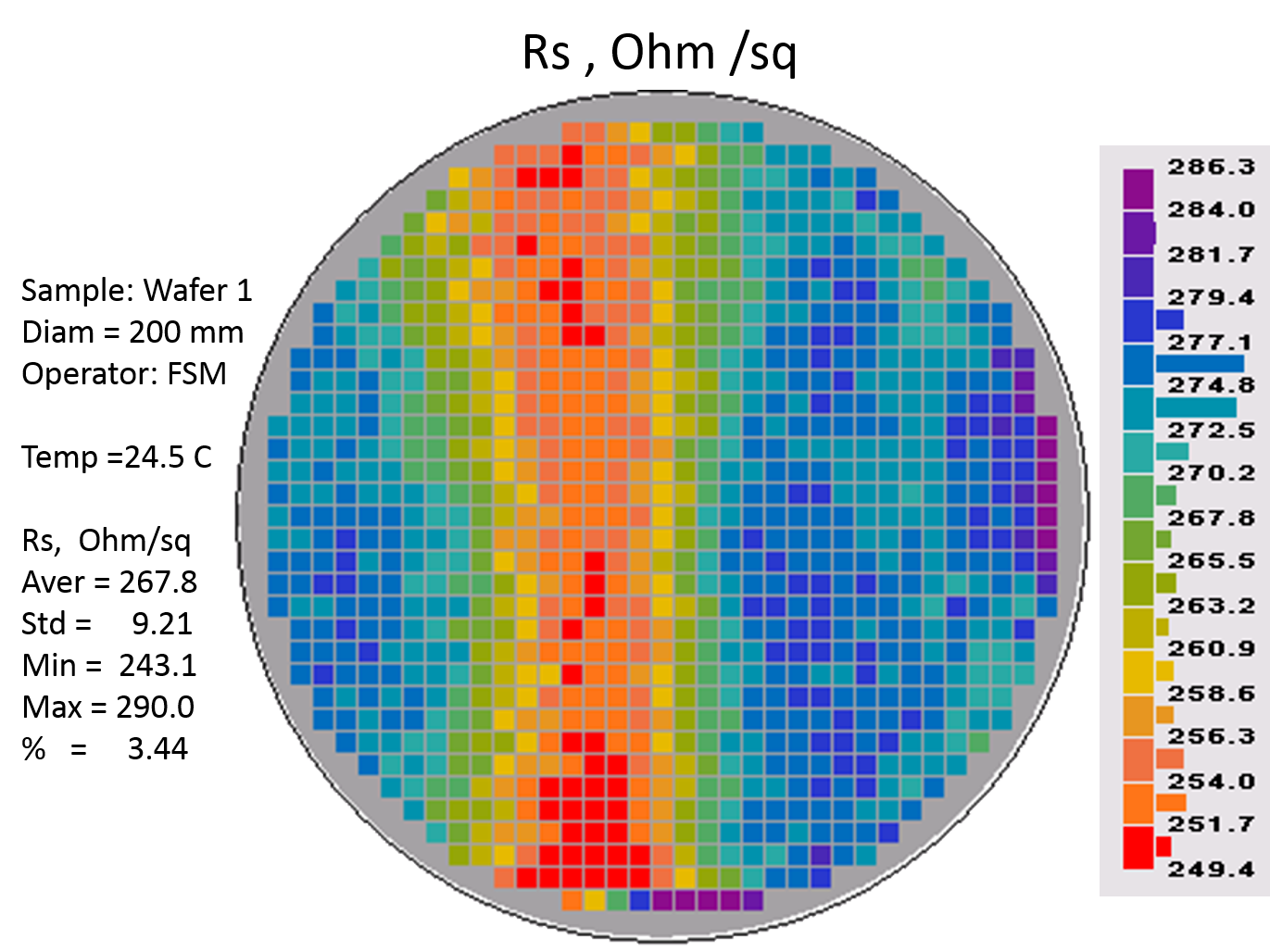

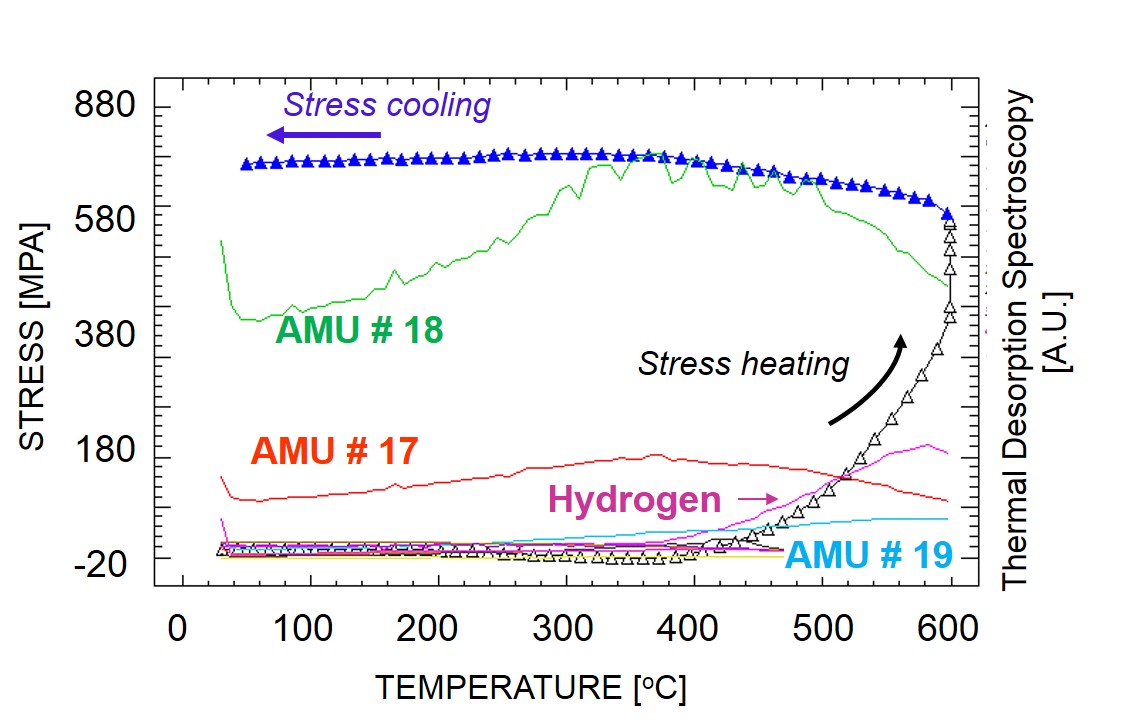

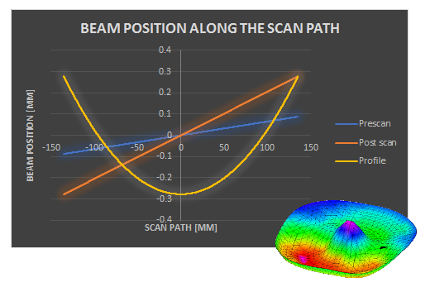

Silicon Concept Inc, (SIC), offers a range of advanced metrology products and solutions for semiconductor, LED, Solar, FPD, Data Storage and MEMS applications. We have over 25 years experience in stress measurement, film adhesion testing, wafer topography metrology, and electrical characterization. Our latest offerings include unique technology to meet the metrology needs of 3DIC manufacturing and to monitor stress of large flat panels.

SIC has local sales and support offices in all major semiconductor clusters. Other areas are covered by a network of local representatives.